УДК 681.511.46

А.Г. Корченко, Л.Г. Черныш

## БЫСТРОДЕЙСТВУЮЩИЙ ВЫЧИСЛИТЕЛЬ ДЛЯ РЕАЛИЗАЦИИ НЕЧЕТКИХ АРИФМЕТИЧЕСКИХ ОПЕРАЦИЙ

Рассмотрены вопросы построения аппаратных средств, предназначенных для реализации нечетких арифметических операций. Предложены структуры устройств, выполняющих указанные операции по методу линейной аппроксимации по локальным максимумам.

При решении различных прикладных задач, основывающихся на теории нечетких множеств, требуется выполнять большое число нечетких арифметических операций (НАО), например, при решении систем линейных алгебраических уравнений с нечеткими коэффициентами. В работе [1] предложены НАО с линейной аппроксимацией по локальным максимумам (ЛАЛМ), которые целесообразно применять при решении указанных задач. Эти операции состоят из трех процедур.

Процедура 1. Выполнение максминной композиции (ММК) и формирование отношения порядка (  $\mathbf{z}_{k}^{(l)} < \mathbf{z}_{k+1}^{(l)}$  ), в результате которого образуется число:

$$\sum_{i=1}^{Z(1)} = \{ \mu_{z}(z_{i}^{(i)})/z_{i}^{(i)}, ..., \mu_{z}(z_{k}^{(i)})/z_{k}^{(i)}, ..., \mu_{z}(z_{p}^{(i)})/z_{p}^{(i)} \} =$$

$$= \bigcup_{i=1}^{n} \bigcup_{j=1}^{m} \{ \max_{j \neq i} \min_{(\forall \mu: \exists! z_{ij})} \min_{(\mu_{x}(x_{i}), \mu_{y}(y_{j}))/(x_{i} * y_{j}) \},$$

(1)

где  $z_{ij} = x_i$  \*  $y_j$ ;  $p \le n \times m$ , a \* - одна из арифмегических операций "+", "-", "х", ":". Процедура 2. Аппроксимация значения  $\underbrace{Z}^{(1)}$  числом  $\underbrace{Z}^{(2)}$  по формуле:

$$\sum_{i=1}^{Z(1)} \sum_{k=2}^{Z(2)} = \left\{ \mu_{z}(z_{i}^{(2)})/z_{i}^{(2)}, ..., \mu_{z}(z_{i}^{(2)})/z_{i}^{(2)}, ..., \mu_{z}(z_{f}^{(2)})/z_{f}^{(2)} \right\} =$$

$$= \left\{ \mu_{z}(z_{i}^{(2)})/z_{i}^{(2)}, \bigcup_{\substack{k=2\\(Q=1)}}^{p-1} \mu_{z}(z_{k}^{(1)})/z_{k}^{(1)}, \mu_{z}(z_{p}^{(1)})/z_{p}^{(1)} \right\},$$

(2)

где  $\Omega$ =1 - условие аппроксимации.

Процедура 3. Определение Z, согласно процедуре 2, при уловии, что  $\dim(Z^{\binom{1}{\gamma}}) \neq \dim(Z^{\binom{1}{\gamma+1}})$  ( $\gamma = 1, 2, 3, ...$ ).

В работах [2, 3, 4] были предложены аппаратные средства, используемые для организации нечетких вычислителей. Для реализации НАО с ЛАЛМ предлагается нечеткий

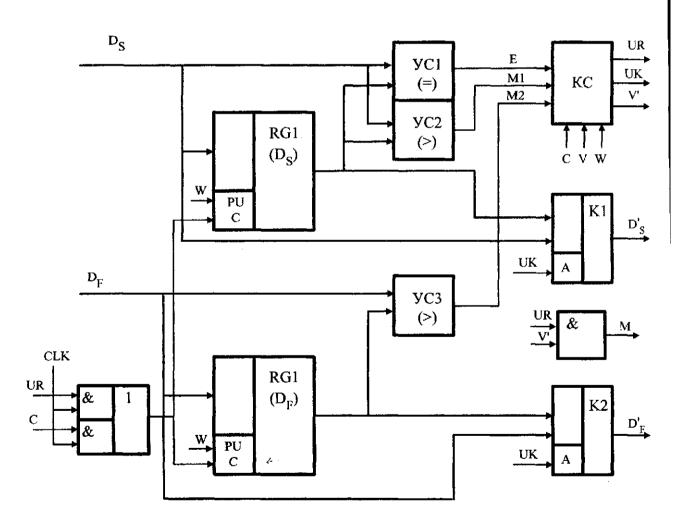

аппроксимационный вычислитель, выполняющий четыре основные арифметические операции. Для его построения необходимо модифицировать максминторную запоминающую ячейку (ММҮ) [2] путем расширения логических функций. Структурная схема такой ММҮ показана на рис.1. В отличие от исходной ячейки в рассматриваемую дополнительно введены устройство сравнения 2 (УС2) для определения большего числа и конъюнктор для формирования выходного сигнала М записи в ММҮ. Модифицированная ММҮ функционирует в соответствии с булевскими выражениями, полученными на основе таблицы переходов (см. таблицу):

$$\begin{aligned} & \text{UR} = \overline{C} \wedge V \wedge \left( W \wedge \overline{E} \wedge M1 \vee \overline{W} \wedge \overline{E} \wedge \overline{M1} \vee E \wedge \overline{M_1} \wedge M2 \right); \\ & \text{UK} = \overline{C} \wedge V \wedge \left( W \wedge \overline{M1} \vee \overline{W} \wedge M1 \right); \\ & \text{V'} = \overline{C} \wedge V \wedge \overline{E}; \\ & \text{M} = \text{UR} \wedge \text{V'}. \end{aligned}$$

Рис. 1. Структурная схема модифицированной ММУ

Управление работой данной ММУ осуществляется по аналогии с исходной, функционирование которой описано в работе [2].

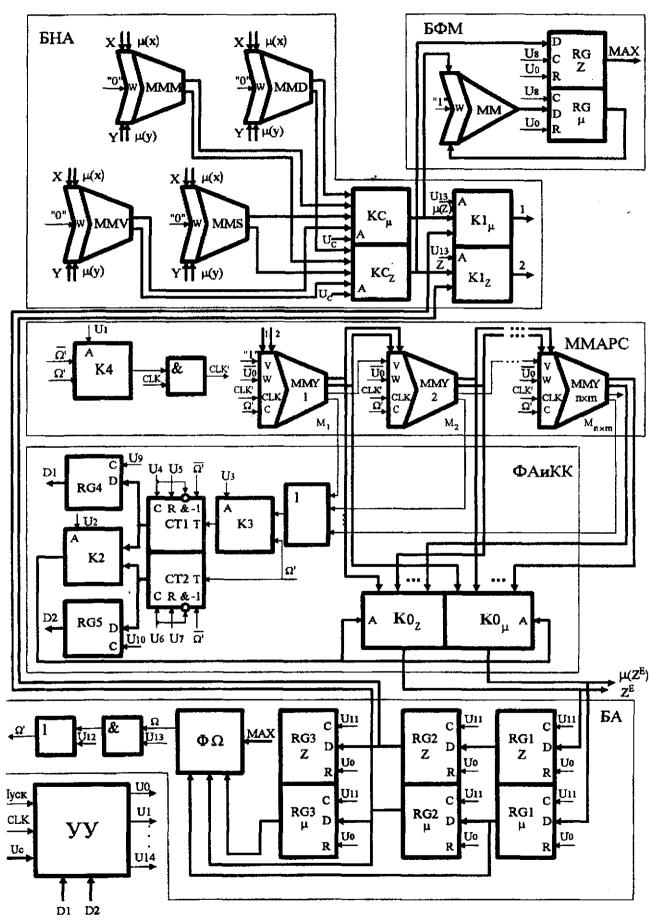

Нечеткий аппроксимационный вычислитель показан на рис.2. Он содержит блоки нечеткой арифметики (БНА), формирования максимума (БФМ) и аппроксимации (БА),

максминный аппроксимационный регистр сдвига (ММАРС), формирователь адресов и количества компонент (ФАиКК), а также устройство управления (УУ).

Блок нечетной арифметики предназначен для выполнения максминных арифметических операций (ММАО) типа умножения, сложения, вычитания и деления, которые реализуются соответственно максминторными умножителем (МММ), сумматором (ММS), вычитателем (ММV) и делителем (ММD) [2].

| Таб | лица | переходов |

|-----|------|-----------|

|     |      |           |

|                 |   |   |   |    | T-P-11-0,C |    |    |    |    |

|-----------------|---|---|---|----|------------|----|----|----|----|

| Номер состояния | C | V | W | E  | M1         | M2 | UR | UK | V' |

| 0-15            | 0 | 0 | * | *  | * *        | *  | 0  | *  | 0  |

| 16              | 0 | 1 | 0 | 0  | 0          | 0  | 1  | 0  | 1  |

| 17              | 0 | 1 | 0 | 0  | 0          | 1  | 1  | 0  | 1  |

| 18              | 0 | 1 | 0 | 0  | 1          | 0  | 0  | 1  | 1  |

| 19              | 0 | 1 | 0 | 0  | 1          | 1  | 0  | 1  | 1  |

| 20              | 0 | 1 | 0 | 1  | 0          | 0  | 0  | *  | 0  |

| 21              | 0 | 1 | 0 | _1 | 0          | 1  | 1  | *  | 0  |

| 22              | 0 | 1 | 0 | 1  | 1          | 0  | 0  | *  | 0  |

| 23              | 0 | 1 | 0 | 1  | 1          | 1  | 0  | *  | 0  |

| 24              | 0 | 1 | 0 | 0  | 0          | 0  | 0  | 1  | 1  |

| 25              | 0 | 1 | 1 | 0  | 0          | 1  | 0  | 1  | 1  |

| 26              | 0 | 1 | 1 | 0  | 1          | 0  | 1  | 0  | 1  |

| 27              | 0 | 1 | 1 | 0  | 1          | 1  | 1  | 0  | 1  |

| 28              | 0 | 1 | I | 1  | 0          | 0  | 0_ | *  | 0  |

| 29              | 0 | 1 | 1 | 1  | 0          | 1  | 1  | *  | 0  |

| 30              | 0 | 1 | 1 | 1  | 1          | 0  | 0  | *  | 0  |

| 31              | 0 | 1 | 1 | 1  | 1          | 1  | 0  | *  | 0  |

| 32-63           | 1 | * | * | *  | *          | *  | 0  | *  | 0  |

Примечание. Символ "\*" обозначает любое состояние.

Блок формирования максимума служит для определения компоненты нечеткого числа (НЧ) Z с максимальной функцией принадлежности.

Максиминный аппроксимационный регистр сдвига хранит и обрабатывает результаты ММАО и результаты аппроксимационной обработки.

Устройство ФАиКК формирует исходные данные для УУ и коммутирует выходы ММАРС на БА.

Блок аппроксимации предназначен для аппроксимационной обработки (в соответствии с процедурой 2 и 3) и формирования признака аппроксимации  $\Omega$ .

Устройство управления вырабатывает управляющие сигналы  $U_0,\,U_1,\,...,\,U_{14}$  на основе сигналов D1 и D2, поступающих от блока  $\Phi$ AиКК.

Вычислитель работает следующим образом.

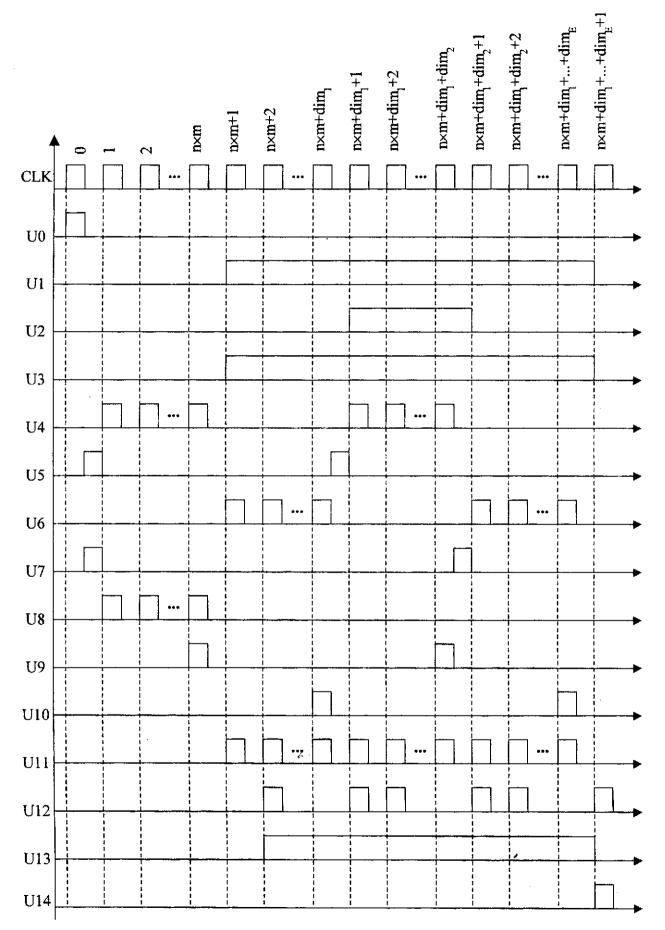

Перед началом вычислительного процесса по переднему фронту нулевого синхроимпульса СLК (рис.3) происходит сброс всех регистров БА, БФМ и ММY<sub>i</sub> ( $i=\overline{1,n\times m}$ ) ММАРС ( $U_0=1$ ), по заднему фронту которого сбрасываются счетчики СТ1 и СТ2 ( $U_5=U_7=1$ ). В УУ поступает двухразрядный код  $U_C$ , по которому осуществляется выбор МММ, ММS, ММV или ММD. На пары входных шин X,  $\mu(x)$  и Y,  $\mu(y)$  покомпонентно поступают значения НЧ X и Y:

$$X = \{\mu_x(x_1) / x_1, ..., \mu_x(x_i) / x_i, ..., \mu_x(x_n) / x_n\},\$$

$$\label{eq:equation:equation:equation:equation} \underbrace{Y} = \{ \mu_y(y_1) / y_1, \, \dots \, , \, \mu_y(y_j) / y_j, \, \dots \, , \, \mu_y(y_m) / y_m \}.$$

В соответствии с временной диаграммой (рис.3) через коммутаторы  $KC_{\mu}$ ,  $KC_{Z}$  и  $K1_{\mu}$ ,  $K1_{Z}$  в ячейки ММҮ последовательно (по сигналу CLK') поступают  $n\times m$  компонент, образованных в результате выбранной ММАО в соответствии с выражением

$$\bigcup_{i=1}^n \bigcup_{j=1}^m \{ \max \min \left( \mu_x(x_i) \,,\, \frac{\mu_y(y_j)}{} \right) / \left( x_i \textcircled{*} y_j \right) \} \ (\text{см. процедуру 1}).$$

За первые n×m тактов в MMAPC осуществляется MMK в соответствии с процедурой 1, а число импульсов CLK' (управляющих работой MMY) равно числу импульсов CLK, поскольку на вход конъюнктора с выхода коммутатора K4 поступает сигнал  $\overline{\Omega}'$ =1 (U<sub>1</sub>=0). При этом на управляющий вход C всех MMY подается  $\Omega'$ =0 (так как U<sub>12</sub>=U<sub>13</sub>=0). За этот же промежуток времени в БФМ посредством максминтора (MM) [2] осуществляется поиск компоненты с максимальной функцией принадлежности, которая заносится в регистры RG<sub>µ</sub> и RG<sub>Z</sub> по синхросигналу U<sub>8</sub>, а счетчик CT1 подсчитывает количество компонент, образованных в результате выполнения процедуры 1. Содержимое счетчика увеличивается на единицу в том случае, если в ячейки MMAPC была занесена очередная компонента и сформировался сигнал записи в ячейку M<sub>i</sub> (i =  $\overline{1}$ , n × m), который поступает на синхровход Т (тактируемый сигналом U<sub>4</sub>) CT1 через дизьюнктор и коммутатор K3 (U<sub>3</sub>=0). Отметим, что счетчики CT1 и CT2 имеют, кроме указанного выше синхровхода, счетный асинхронный вход "-1", уменьшающий содержимое на единицу и имеющий расширение по "И" (то есть выполняется функция, управляющая указанным входом в соответствии с выражениями  $\overline{\Omega}' \wedge \overline{U}_4$  для CT1 и  $\overline{\Omega}' \wedge \overline{U}_6$  для CT2).

По n×m такту значение на выходе CT1 по сигналу U<sub>9</sub>=1 заносится в регистр RG4 и по сигналу U<sub>2</sub>=0 через коммутатор K2 подключается к адресному входу коммутаторов K0<sub> $\mu$ </sub> и K0<sub> $\mu$ </sub>, которые соединяют ячейку со значением  $\mu_z(z_t^{(2)})/z_t^{(2)}$  (см. процедуру 2) со входами регистров RG1 $\mu$  и RG1 $_{\pi}$ .

По такту  $n \times m+1$  коммутаторы К3 и К4 передают сигнал  $\Omega'$  ( $U_1=U_3=1$ ), который управляет работой СТ1 и СТ2, формирует сигнал СLК' и поступает на управляющий вход ММҮ. По сигналу  $U_{11}=1$  в RG1 $_{\mu}$  и RG1 $_{Z}$  заносится входная информация. Поскольку  $\overline{\Omega}'=1$ ,  $U_4=\overline{U_6}=0$ , то содержимое СТ1 в указанном такте уменьшается на единицу, а содержимое СТ2 не изменяется.

По такту  $n \times m + 2$   $K1_{\mu}$  и  $K1_{Z}$  коммутируют выходные шины регистров  $RG2_{\mu}$  и  $RG2_{Z}$  БА  $(U_{13}=1)$  с целью организации обратной связи БА и ММАРС, при этом значение  $\Omega'=1$   $(U_{12}=1)$ .

До такта  $n \times m + dim_1$  включительно входы C CT2 и  $RG1_\mu$ ,  $RG1_Z$ ,  $RG2_\mu$ ,  $RG2_Z$ ,  $RG3_\mu$ ,  $RG3_Z$  синхронизируются сигналами  $U_6$  и  $U_{11}$  соответственно. Значение сигнала  $\Omega$ , от которого зависит значение  $\Omega'$ , формируется блоком  $\Phi\Omega$  БА, в котором осуществляется анализ очередной триады значений, поступивших с MMAPC и значения MAX, сформированного в БФМ в соответствии с процедурой 2.

По  $n \times m + dim_1$  такту CT1 сбрасывается (U<sub>5</sub>=1), а содержимое CT2 заносится в RG5 (U<sub>10</sub>=1).

Рис.2. Структурная схема нечетко аппроксимационного вычислителя

Рис.3. Временная диаграмма работы нечетко аппроксимационного вычислителя

По п×m+dim $_1$ +1 такту содержимое СТ2 в соответствии с сигналом  $U_2$ =1 через К2 поступает на адресный вход К $0_\mu$  и К $0_z$ , при этом  $U_4$ =1, а  $U_6$ =0. По сигналу  $U_{12}$ =1 значение  $\mu_z(z_1^{(2)})/z_1^{(2)}$  (см. пропедуру 2) передается по обратной связи в ММАРС. На этом заканчивается выполнение процедуры 2. Таким образом, вычислительный процесс повторяется в соответствии с процедурой 3 E раз с чередованием функций СТ1 и СТ2 до момента, когда значения D1 и D2 на выходах RG4 и RG5, поступающие на УУ, не станут равными. Равенство D1 и D2 является командой УУ для выработки сигнала  $U_{14}$ =1 ("Стоп"), соответствующего  $n\times m+dim_1+\ldots+dim_E+1$  такту временной диаграммы. Теперь на выходные шины  $\mu(Z^E)$  и  $Z^E$  потактно (за D1=D2 синхроимпульсов) осуществляется передача результата Z НАО с ЛАЛМ с ячеек ММАРС.

Данное устройство можно использовать для построения сопроцессоров нечеткой арифметики, которые могут применяться совместно с универсальным процессором для повышения скорости вычислений, а также в качестве расширителя функциональных возможностей вычислительных машин.

## Список литературы

- 1. Корченко А.Г. Нечеткие арифметические операции с линейной аппроксимацией по локальным максимумам. // Збірник наукових праць інституту проблем моделювання в енергетиці. Львів: Світ, 1998. Вип. 4. С. 3-6.

- 2. Аль-Хадиди М.М., Корченко А.Г., Скворцов С.А. Диагностирование вычислительных структур на основе нечетких операций. // Киев, 1993. 26 с. (Препр. 93-62 ИПМЭ АН Украины).

- 3. *Корченко А.Г.* Методы и аппаратные средства реализации нечетких операций.// Автоматизированные системы обработки информации: Сб. науч. тр. К.: КМУГА, 1996. С.17-25.

- 4. Черныш Л.Г. Максминторный сепаратор нечетких вычислителей для диагностических систем реального времени. // Автоматизированные системы обработки информации: Сб. науч. тр. К.: КМУГА, 1996. С.107-110.

Стаття надійшла до редакції 3 березня 1999 року.

Корченко Олександр Григорович (1961) закінчив КІЩА в 1983 році. Кандидат технічних наук, доцент кафедры основ обчислювальної техніки та бортових обчислювальних систем Київського міжнародного університету цивільної авіації. Автор більш як 50 наукових праць в області підвищення швидкодії засобів обчислювальної техніки, інформаційної безпеки та використання теорії нечітких множин для рішення прикладних задач.

Alexander G. Korchenko (b. 1961) graduated from Kyiv Institute of Civil Aviation Engineers (1983). PhD (Eng), ass. professor of Fundamentals of computer machines and on-Board Computers Department of Kyiv International University of Civil Aviation. Author of more than 50 publications in the field of increasing of the computer facilities speed, information safety and use of the fuzzy sets theory for solution of the application tasks.

Леся Григорівна Черниш (1973) закінчила КМУЦА в 1995 році. Аспірантка кафедры основ обчислювальної техніки та бортових обчислювальних систем Київського міжнародного університету цивільної авіації. Працює над теорією нечітких множин в області безпеки інформації.

Lesya G. Chernish (b. 1973) graduated from Kyiv International University of Civil Aviation (1995). Post-graduate student of Kyiv International University of Civil Aviation. Specializes in the field of application of fuzzy sets theory in the information safety