UDC 621.317.7 (045)

I. Yu. Sergeyev

# ANALYSIS OF THE POTENTIATION DIGITAL-TO-ANALOG CONVERTER WITH ACCOUNTING OF IMPERFECTION ITS BLOCKS

Department of Aviation Computer-Integrated Complexes, National Aviation University, Kyiv, Ukraine E-mail: sergeyevi@i.ua

**Abstract**—Potentiation digital-to-analog converter with iterative additive correction of errors is described. Analysis of errors of this converter with accounting of imperfection its blocks was produced. Basic expressions for the calculation of these errors are listed. The obtained equations conversion and carried out error analysis allow to create high-precision potentiation digital-to-analog converter.

**Index Terms**—integrator; potentiation digital-to-analog converter; iteratively additive correction of errors; imperfection of blocks; dynamics of the iterative process.

#### I. INTRODUCTION

It is known that achievement of high linearity transformation functions of information systems related to the collection, processing and transmission of information depends on metrological parameters of the measuring converters used in such information systems, and consequently independence of it's static transformative characteristics from measured value.

Reduction of level of measuring converters error often plays a decisive role in solving the problem of creation of information systems such as automated information-measuring systems, automated control systems, pattern recognition, diagnosis or identification.

### II. PROBLEM STATEMENT

In work [1] the measuring converter offered by the author [2], [3] has been considered. It is an iteratively integrating code-voltage converter with additive correction of errors.

If to speak about this measuring converter from the point of view of his function of transformation, then it is the DAC, in which the output voltage is directly proportional to the input code given in decibels.

In work [1] are considered the equation of transformation and the main equations for definition of errors of this measuring converter without accounting of imperfection of it's components (blocks).

However, in the course of design of the measuring converter it isn't enough. In this case we need to have the main equations with taking into account of not ideality of components of the considered measuring converter.

Derivation of such equations is the main objective of this work.

# III. MAIN EQUATIONS WITHOUT TAKING INTO ACCOUNT OF IMPERFECTION OF BLOCKS

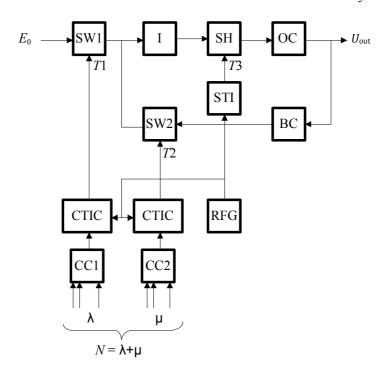

The structural scheme of iteratively integrating code-voltage converter with additive correction of errors is shown in Fig. 1.

Here I is integrator; SH is sample-and-hold device; SW1 and SW2 are analog keys; RFG is reference frequency generator; CC1 and CC2 are code converters; CTIC1 and CTIC2 are converters of code into the time intervals; STI is shaper of time intervals;  $E_0$  is reference voltage;  $N = \lambda + \mu$  are the input code;  $U_{\text{out}}$  is output voltage; OC is output converter, BC is back converter.

For convenience the equation of transformation and the main equations for definition of errors of this measuring converter without not ideality of his components are given below.

Nonlinearity which is realized in the converter corresponds to the operation of potentiation, i.e. function which is inverse to obtaining logarithm. The input code is given in decibels (dB).

Output voltage value relative to a value of  $U_0$ , corresponding to input code N = 0 dB:

$$N (dB) = 20 \lg U_{out} / U_0$$

.

Equation of converting of this potentiation converter:

$$U_{\text{out}} = U_0 10^{N/20}$$

.

If the submit an input code N as the sum of two terms (for example, integers and tenths)  $N = \lambda + \mu$ , conversion equation can be transformed to:

$$U_{\rm out} = U_0 10^{\lambda/20} / 10^{-\mu/20}$$

.

After the ending of the first and second conversion cycles the output voltage  $U_{\rm out}$  is equal to:

$$U_1 = (E_0 \lambda K_{\lambda} K_{SH} K_{RP} K_A / f_0 RC) - U_0 Q_H$$

and

$$U_2 = (E_0 \lambda K_{\lambda} K_{SH} K_{RP} K_A / f_0 RC) (1 - Q_H) - U_0 Q_H,$$

respectively, where:  $K_{\lambda}$ ,  $K_{\mu}$ ,  $K_{SH}$  and  $K_{RP}$ ,  $K_{A}$ ,  $K_{VD}$  – are transfer coefficients of the devices CC1, CC2,

SH, OC and BC respectively,  $f_0$  is reference frequency; R and C resistance and capacitance of integrator's resistor and capacitor respectively; and

$$Q_{\rm H} = 1 - \mu K_{\rm H} K_{\rm SH} K_{\rm RP} K_{\rm A} K_{\rm VD} / f_0 RC.$$

Output voltage of the code-voltage converter after the end of *n*th cycle;  $j = \overline{1,n}$ :

$$\begin{split} \boldsymbol{U}_{n} &= (E_{0}\lambda\boldsymbol{K}_{\lambda}\boldsymbol{K}_{\mathrm{SH}}\boldsymbol{K}_{\mathrm{RP}}\boldsymbol{K}_{\mathrm{A}} / f_{0}R\boldsymbol{C})\sum_{\mathrm{j=1}}^{n}\boldsymbol{Q}_{\mathrm{H}}^{\mathrm{j-l}} - \boldsymbol{U}_{0}\boldsymbol{Q}_{\mathrm{H}}^{n} \\ &= \frac{E_{0}\lambda\boldsymbol{K}_{\lambda}}{\mu\boldsymbol{K}_{\mathrm{UD}}}(1 - \boldsymbol{Q}_{\mathrm{H}}) - \boldsymbol{U}_{0}\boldsymbol{Q}_{\mathrm{H}}^{n} = \boldsymbol{U}_{\infty} - \Delta\boldsymbol{U}\boldsymbol{Q}_{\mathrm{H}}^{n}. \end{split}$$

where  $U_n$  is output voltage of the code-voltage converter after the end of nth cycle;  $j = \overline{1, n}$ .

Fig. 1. Potentiation digital-to-analog converter

If the condition  $|Q_{\rm H}| < 0$  is fulfilled, output voltage of the potentiation digital-to-analog converter at the steady-state condition  $(n \rightarrow \infty)$  is determined by the expression

$$\begin{split} U_{\infty} = & \frac{E_0 \lambda K_{\lambda}}{\mu K_{\mu} K_{\text{VD}}} \\ = & \frac{E_0}{K_{\text{VD}}} 10^{(\lambda + \mu)/20}, \end{split}$$

where

$$K_{\lambda} = \frac{10^{\lambda/20}}{\lambda}, \qquad K_{\mu} = \frac{10^{-\mu/20}}{\mu}.$$

The relative error of conversion  $\gamma_n$ :

$$\gamma_n = \frac{U_n - U_{\infty}}{U_{\infty}} = \frac{\Delta U Q_{\rm H}^n}{U_{\infty}},$$

where  $\Delta U = U_{\infty} - U_0$ .

Number of cycles n, corresponding to this error  $\gamma_n$ :

$$n = \left\lceil \frac{\ln \left| \frac{\gamma_n U_{\infty}}{\Delta U} \right|}{\ln \left| Q_{\rm H} \right|} \right\rceil + 1.$$

Basic expressions for the iteratively integrating code-voltage converter with additive correction of errors with taking into account of imperfection it's blocks are summarized in Table 1-3 (details of the derivation of these expressions, as well as others discussed below, can be found in work [2]).

IV. EQUATIONS WITH TAKING INTO ACCOUNT OF IMPERFECTION OF INTEGRATOR'S STATIC PARAMETERS AND OF IMPERFECTION OF BACK CONVERTER

To take into account the effect of the additive and multiplicative errors  $\Delta E_0$ ,  $\Delta_I$ ,  $\Delta_{\rm VD}$ ,  $\gamma_E$ ,  $\gamma_{\rm VD}$ , respectively, reference voltage source  $E_0$ , an integrator I and a back converter BC, the error of the time intervals T1 and T2 formation and it's jitter, we use the results obtained in [1], expressions, denoting,

respectively, through  $\delta T1$ ,  $\delta T2$ ,  $\delta \tau_{Up1}$ ,  $\delta \tau_{Dn1}$ ,  $\delta \tau_{Up2}$ ,  $\delta \tau_{Dn2}$  the relative errors of interval T1 and T2 formation, and relative increment of duration of the rise and fall of current through the SW1 and SW2 keys.

Curves rise and fall times of the currents flowing through the SW1 and SW2 keys when switching we approximate by straight line segments. Whereby the effective time from the point of view of forming volt-second area for T1 and T2, respectively, equal to

$$T1' = T1 - \frac{\tau_{\text{Up1}} - \tau_{\text{Dn1}}}{2}, \quad T2' = T2 - \frac{\tau_{\text{Up2}} - \tau_{\text{Dn2}}}{2}.$$

where  $\tau_{Up1}$ ,  $\tau_{Dn1}$ ,  $\tau_{Up2}$  and  $\tau_{Dn2}$  are rise and fall times of the currents flowing through the SW1 and SW2 keys when switching with the approximation, respectively.

The expressions obtained for determining the output voltage in the steady state  $U_{\rm \infty M}$  and  $U_{\rm \infty A}$  with the multiplicative and additive errors,

respectively, and the corresponding relative errors  $\gamma_{STM}$  and  $\gamma_{STA}$  are shown below, where  $\Delta_I$  and  $\Delta_{VD}$  are additive errors of the integrator I and the back converter BC given to the inputs of the respective blocks.

$$\begin{split} U_{\infty \mathrm{M}} &= \frac{E_0 T \mathrm{I} (1 + \gamma_E)}{K_{\mathrm{VD}} T 2 (1 + \gamma_{\mathrm{VD}})} \\ &\approx \frac{E_0 T \mathrm{I}}{K_{\mathrm{VD}} T 2} (1 + \gamma_E - \gamma_{\mathrm{VD}}) = \frac{E_0 T \mathrm{I}}{K_{\mathrm{VD}} T 2} (1 + \gamma_E - \gamma_{\mathrm{VD}}) \,, \\ &\gamma_{\mathrm{STM}} = \frac{U_{\infty \mathrm{M}} - U_{\infty}}{U_{\infty}} = \gamma_E - \gamma_{\mathrm{VD}} \,, \\ &U_{\infty \mathrm{A}} = U_{\infty} \left( 1 + \gamma_{T1} - \gamma_{T2} + \frac{\Delta E_0}{E_0} + \frac{T_C \Delta_I}{E_0 T \mathrm{I}} + \frac{\Delta_{\mathrm{VD}}}{U_{\infty}} \right) \,, \\ &\gamma_{\mathrm{STA}} = -\gamma_{T1} + \gamma_{T2} - \frac{\Delta E_0}{E_0} - \frac{T_C \Delta_I}{E_0 T \mathrm{I}} - \frac{\Delta_{\mathrm{VD}}}{U_{\infty}} \,, \end{split}$$

where

$$\gamma_{T1} = \frac{T18T1}{T1 - \frac{\tau_{\rm Up1} - \tau_{\rm Dn1}}{2}} + \frac{\frac{\tau_{\rm Up1}}{2} \delta \tau_{\rm Up1} - \frac{\tau_{\rm Dn1}}{2} \delta \tau_{\rm Dn1}}{T1 - \frac{\tau_{\rm Up1} - \tau_{\rm Dn1}}{2}} \approx \delta T1 + \frac{\tau_{\rm Up1} \delta \tau_{\rm Up1} - \tau_{\rm Dn1} \delta \tau_{\rm Dn1}}{2T1},$$

$$\gamma_{T2} = \frac{T2\delta T2}{T2 - \frac{\tau_{\mathrm{Up2}} - \tau_{\mathrm{Dn2}}}{2}} + \frac{\frac{\tau_{\mathrm{Up2}}}{2} \, \delta \tau_{\mathrm{Up2}} - \frac{\tau_{\mathrm{Dn2}}}{2} \, \delta \tau_{\mathrm{Dn2}}}{T2 - \frac{\tau_{\mathrm{Up2}} - \tau_{\mathrm{Dn2}}}{2}} \approx \delta T2 + \frac{\tau_{\mathrm{Up2}} \delta \tau_{\mathrm{Up2}} - \tau_{\mathrm{Dn2}} \delta \tau_{\mathrm{Dn2}}}{2T2} \, .$$

# V. EQUATIONS WITH TAKING INTO ACCOUNT OF IMPERFECTION OF ANALOG KEYS

To take into account of imperfection of keys lets denote resistance of the opened keys SW1 and SW2 as  $R_{10}$  and  $R_{20}$ , and resistance of the closed keys as  $R_{10}$  and  $R_{20}$ , respectively.

Equations for determining the output voltage in the steady state  $U_{\infty RI}$ , the relative errors of output voltage in the *n*th cycle  $\gamma_{nRI}$  and in the steady state  $\gamma_{St\,RI}$  in view of these resistances of keys SW1 and SW2 [5], [6] are shown below.

$$U_{\infty \mathrm{RI}} = \frac{E_0 \left( \frac{\lambda K_{\lambda}}{R + R_{\mathrm{IO}}} + \frac{\mu K_{\mu}}{R + R_{\mathrm{IC}}} \right)}{K_{\mathrm{VD}} \left( \frac{\mu K_{\mu}}{R + R_{\mathrm{2O}}} + \frac{\lambda K_{\lambda}}{R + R_{\mathrm{2C}}} \right)}$$

$$\gamma_{nRI} = \frac{U_{nRI} - U_{\infty RI}}{U_{\infty RI}} = \frac{\Delta U_{RI} Q_{HRI}^n}{U_{\infty RI}}$$

$$\gamma_{\rm St\,Rl} = \frac{U_{\infty \rm Rl} - U_{\infty}}{U_{\infty \rm Rl}} = \frac{\mu K_{\mu} \left( \frac{\lambda K_{\lambda}}{R + R_{\rm IO}} + \frac{\mu K_{\mu}}{R + R_{\rm IC}} \right)}{\lambda K_{\lambda} \left( \frac{\mu K_{\mu}}{R + R_{\rm 2O}} + \frac{\lambda K_{\lambda}}{R + R_{\rm 2C}} \right)},$$

where

$$\begin{split} Q_{\rm HRI} = & \, 1 - \frac{K_{\rm SH} \, K_{\rm RP} K_{\rm A} K_{\rm VD}}{C f_0} \Bigg( \frac{\mu K_{\mu}}{R + R_{\rm 2O}} + \frac{\lambda K_{\lambda}}{R + R_{\rm 2C}} \Bigg), \\ & \Delta U_{\rm RI} = U_{\infty \rm RI} - U_{\infty}. \end{split}$$

VI. CONCLUSION

Potentiation digital-to-analog converter, i.e. DAC, in which the output voltage is directly proportional to the input code given in decibels, based on iteratively integrating code-voltage converter with iterative additive correction of errors, is considered. Analysis of errors of this converter with accounting of imperfection its blocks was produced. Test results and operation experience confirmed the correctness

of the results of theoretical research. Basic expressions for the calculation of these errors are listed and it allow you to create such high-precision potentiation digital-to-analog converter.

#### REFERENCES

- [1] I. Sergeyev, Analysis of the Potentiation Digital-to-Analog Converter Without Accounting of Imperfection its Blocks. Electronics and Control Systems, no. 4(46), Kyiv: NAU, 2015. pp. 52–57.

- [2] I. Sergeyev, "Research and Development of Integrating Measurement Converters with the Iterative Additive Correction of Errors," Ph. D. (Engineering) Thesis, Kyiv Politechnical Institute, Kyiv, Ukraine, 1978. (in Russian).

- [3] V. Gubar, I. Sergeyev, and V. Fediv, USSR Patent 661,525, G 06 G, 7/26, 05.05.79. bull. 17 (in Russian).

- [4] Yu. Tuz, Structural Methodsof Impruving Accuracy of Measuring Devices, manual, Kyiv. Vyshcha Shkola, 1976. (in Russian).

- [5] I. Sergeyev, "Analysis of the ADC with a dynamic integrator," *Measurement Equipment*, no.6, pp. 38–40, 1976. (in Russian).

- [6] Yu. Tuz, and I. Sergeyev, "An iterative converter of time interval to the voltage," *Measurement Equipment*, no. 7, pp. 15–17, 1976. (in Russian).

Received January 11, 2016.

## Sergeyev Igor. Ph. D. Associate Professor.

Aviation Computer-Integrated Complexes Department, National Aviation University, Kyiv, Ukraine.

Education: National Technical University "KPI", Kyiv, Ukraine (1973).

Research interests: automation of technological processors, measurement transducers.

Publications: 210. E-mail: sergeyevi@i.ua

# І. Ю. Сергеєв. Аналіз потенціюючого цифро-аналогового перетворювача з урахуванням неідеальностіості його блоків

Розглянуто потенціюючий цифро-аналоговий перетворювач з ітераційною адитивною корекцією похибок. Виконано аналіз похибок цього перетворювача з урахуванням неідеальності його блоків. Отримані рівняння перетворення та проведений аналіз похибок дозволять створити високоточний потенціюючий цифро-аналоговий перетворювач.

**Ключові слова:** інтегратор; потенціюючий цифро-аналоговий перетворювач; ітераційна адитивна корекція похибок; неідеальність блоків; динаміка ітераційного процесу.

### Сергеєв Ігор Юрійович. Кандидат технічних наук. Доцент.

Кафедра авіаційних комп'ютерно-інтегрованих комплексів, Національний авіаційний університет, Київ, Україна.

Освіта: Національний технічний університет України «КПІ», Київ, Україна (1973).

Напрямок наукової діяльності: автоматизація технологічних процесів, вимірювальні перетворювачі.

Кількість публікацій: 210. E-mail: sergeyevi@i.ua

# И. Ю. Сергеев. Анализ потенцирующего цифро-аналогового преобразователя с учетом неидеальности его блоков

Рассмотрен потенцирующий цифро-аналоговый преобразователь с итерационной аддитивной коррекцией погрешности. Выполнен анализ погрешностей этого преобразователя с учетом неидеальности его блоков. Полученные уравнение преобразования и проведенный анализ погрешностей позволят создать высокоточный потенцирующий цифро-аналоговый преобразователь.

**Ключевые слова:** интегратор; потенцирующий цифро-аналоговый преобразователь; итерационная аддитивная коррекция погрешностей; неидеальность блоков; динамика итерационного процесса.

## Сергеев Игорь Юрьевич. Кандидат технических наук. Доцент.

Кафедра авиационных компьютерно-интегрированных комплексов, Национальный авиационный университет, Киев, Украина.

Образование: Национальный технический университет Украины «КПИ», Киев, Украина (1973).

Направление научной деятельности: автоматизация технологических процессов, измерительные преобразователи.

Количество публикаций: 210.

E-mail: sergeyevi@i.ua