UDC 621.386:616-073.7(045)

O. M. Klyuchko, V. I. Tsal-Tsalko

# DEVICE AND SOFTWARE FOR TESTING AND TRAINING OF HUMAN VISUAL MEMORY ON THE BASE OF ATmega32 MICROCONTROLLER

Aeronavigation Institute, National Aviation University, Kyiv, Ukraine E-mail: iesy@nau.edu.ua

**Abstract.** The data about new device with full package of supported program supply for testing and training of human visual memory are suggested. Device is constructed on the base of microcontroller ATmega32 and AVR Studio environment.

**Keywords:** ATmega32 microcontroller; device for memory testing; Program supply; AVR Studio environment.

### Introduction

Problems of further search of novel methods for investigation and perfection of human psycho physiological state, their memory, cognitive functions are important not only for the solution of industrial requests of Ukraine (professional abilities, and etc.), but also for the good adaptation of people (especially elders) and their families. All problems, linked with the memory attracted great attention of investigators during all ages, and especially in contemporary world. Memory is a psychophysiological process by which a person is able to record information in own brain (to remember) with aim to act adequately using past experience (actions, emotions, etc.). Information for memorization is recorded in the cerebral cortex of human brain. Humans with phenomenal memory often have very high IQ. Thus children memory training is rather important for their self development. Different branches of human activities are closed for people with memory disorders. In many countries of the world the works in these directions are provided. Memory damages that may influence negatively at people life quality may be corrected (at least partially), especially if to start such correction in time. Even this brief list of facts evidences about the importance of development of new devices, systems and methods for the perfection of memory functions. The search of new methods more effective and inexpensive for ordinary people is in process.

Developments of device and method described in this article below have to help in solution of mentioned problems. Because the most effective is visual memory, and more then 90 % of our memories are visual, new device for memory testing and training (DMTT) acts through the visual analytic system. DMTT and program supply for it permit us to test human memory in quantitative values. Besides of all

its preferences DMTT is enough inexpensive that is important for elderly people. All above described characteristics make DMTT important and convenient for domestic use as well as for such professional branches as dispatchers, rescuers, scientists and others.

#### Task statement

To develop new device DMTT with the package of program supply for testing and training of human visual memory on the base of microcontroller AT-mega32 and AVR Studio environment.

# Main part. Steps of DMTT and software development

Processes of development of DMTT and software for it were realized into few steps. Here is the sequence of fulfilled work steps. 1. Development of the electrical schemes using applications of personal computer. 2. Implementation of board arrangement for device. 3. Provision of software support for microcontroller ATmega32. 4. Provision of software support for LCD module.

As method for development of electrical scheme the Proteus application was used. To implement software support for microcontroller AVR Studio was applied.

# The overview of AVR ATmega for purpose of DMTT construction

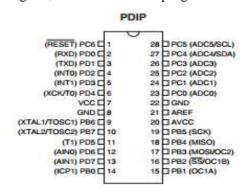

The Atmel AVR ATmega8 is a low-power CMOS 8-bit microcontroller based on the AVR RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega8 achieves throughputs approaching 1MIPS per MHz, allowing the system designer to optimize power consumption versus processing speed (fig. 1).

The ATmega8 provides the following features: 8 Kbytes of In-System Programmable Flash with

Read-While-Write capabilities, 512 bytes of EE-PROM, 1 Kbyte of SRAM, 23 general purpose I/O lines, 32 general purpose working registers, three flexible Timer/Counters with compare modes, internal and external interrupts, a serial programmable USART, a byte oriented Twowire Serial Interface, a 6-channel ADC (eight channels in TQFP and QFN/MLF packages) with 10-bit accuracy, a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, and five software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Powerdown mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next Interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption.

The device is manufactured using Atmel's high density non-volatile memory technology. The Flash Program memory can be reprogrammed In-System through an SPI serial interface, by a conventional non-volatile memory programmer, or by an On-chip boot program running on the AVR core. The boot program can use any interface to download the application program in the Application Flash memory. Software in the Boot Flash Section will continue to run while the Application Flash Section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega8 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.

The ATmega8 is supported with a full suite of program and system development tools, including *C* compilers, macro assemblers, program debugger /simulators, In-Circuit Emulators, and evaluation kits.

We reviewed the most popular families of a MC. Really, ATmega series is the newest and more suitable to our device. It has a type with 40 pins, more flash memory and it's reliable. The AVR is a modified Harvard architecture machine where program and data is stored in separate physical memory systems that appear in different address spaces, but having the ability to read data items from program memory using special instructions. The Atmel AVR ATmega32 is supported with a full suite of program and system development

tools, including C compilers, macro assemblers, program debugger/simulators, In-Circuit Emulators, and evaluation kits. It has 32 kb of flash memory, so that is good, because our code program is very large.

Fig. 1. Pinout of ATmega8

# **Description of AVR ATmega32**

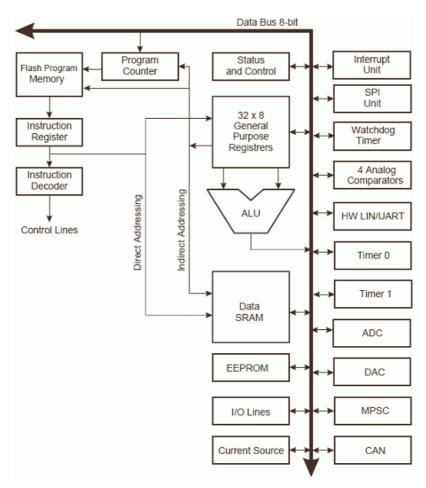

The ATmega32 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega32 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed (fig. 2).

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega32 provides the following characteristics: 32K bytes of In-System Programmable Flash Program memory with Read-While-Write capabilities, 1024 bytes EEPROM, 2K byte SRAM, 32 general purpose I/O lines, 32 general purpose working registers, a JTAG interface for Boundary-scan, On-chip Debugging support and programming, three flexible Timer/Counters with compare modes, Internal and External Interrupts, a serial programmable USART, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain (TQFP package only), a programmable Watchdog Timer with Internal Osc illator, an SPI serial port, and six software selectable power saving modes. The Idle mode stops the CPU while allowing the USART, Two-wire interface, A/D Converter, SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning.

The Power-down mode saves the register con-tents but freezes the Oscillator, disabling all other chip functions until the next External Interrupt or Hardware Reset. In Power-save mode, the Asynchronous Timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping.

The ADC Noise Reduction mode stops the CPU and all I/O modules except Asynchronous Timer and

ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping.

Fig. 2. Functional scheme of MC ATmega32

This allows very fast start-up combined with low-power consumption. In Extended Standby mode, both the main Oscillator and the Asynchronous Timer continue to run. The device is manufactured using Atmel's high density nonvolatile memory technology.

The On-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the Application Flash memory. Soft-ware in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega32 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.

The ATmega32 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger /simulators, in-circuit emulators, and evaluation kits.

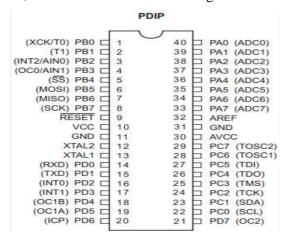

# **Pin Descriptions**

Description is given for pins at fig. 3.

**VCC** Digital supply voltage.

**GND** Ground.

## Port A (PA7...PA0)

Port A serves as the analog inputs to the A/D Converter.

Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. When pins PA0 to PA7 are used as inputs

and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Fig. 3. Pinout of ATmega32

## Port B (PB7...PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

# Port C (PC7...PC0)

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PC5 (TD I), PC3 (TMS) and PC2 (TCK) will be activated even if a reset occurs. The TD0 pin is tri-stated unless TAP states that shift out data are entered.

## Port D (PD7...PD0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

### RESET

Reset Input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.

### XTAL1

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

#### XTAL2

Output from the inverting Oscillator amplifier.

### AVC

AVCC is the supply voltage pin for Port A and the A/D Converter. It should be externally connected to VCC even if the ADC is not used. If the ADC is used, it should be connected to VCC through a low-pass filter

## **AREF**

AREF is the analog reference pin for the A/D Converter. The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed. The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Some implementations of the architecture also provide a powerful multiplier supporting both signed/unsigned multiplication and fractional format.

# Overview of AVR Studio. AVR C++

AVR Studio is the new integrated development environment from Atmel. It provides you a modern and powerful environment for doing AVR development. All 8-bit and 32-bit microcontrollers are supported. Let's start by exploring the included example projects. Run your solution on a starter or evaluation kit. Program and debug your project with the included simulator, or use one of the powerful on-chip debugging and programming tools from Atmel. Get productive with the various navigate, refactor and intellisense features in the included editor. Experience seamless integration with various Atmel WEB services like Atmel Video Lounge, Atmel Store and datasheets to keep you updated and help you to design your solutions.

With strong extension possibilities and online gallery, it is possible for both designers and 3rd party to provide plug-ins and customize the environment for best use and productivity. AVR Studio carries and integrates the AVR GCC toolchain, AVR Software framework, assembler and simulator. All newest

Atmel tools are supported including AVR ONE!, JTAGICE, JTAGICE3, STK500, STK600, QT600, AVRISP mkII and AVR Dragon.

C++ was designed to support data abstraction and object-oriented programming in addition to the traditional style of C. However, this does not mean that the language demands of any one style of programming from all users. C++ is now considered the dominant language used for processing developed commercial software products and we picked up it for our purposes realization.

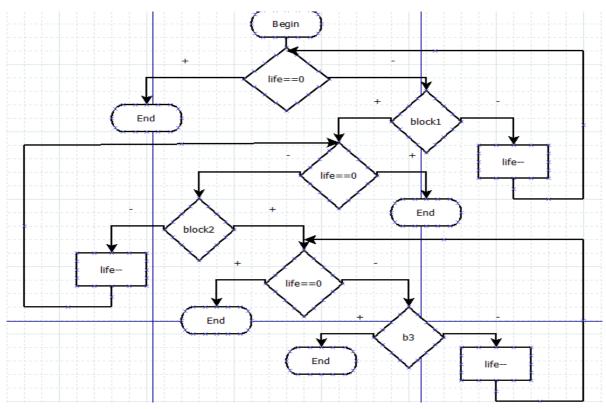

# Algorithm of the program

The sense of device functioning is following: in a random order LEDs are turned on (fig. 4). After LEDs are blow out, the user have to repeat the order of LEDs. There are 10 difficulties in a test. Most hard is the last one. User has 3 tries, after this he will lose and LCD module will show the result of user's activity. The result is calculated using formula:

result=

$$\frac{\text{pLED}}{\text{tLED}}$$

100%,

where, pLED – is a passed LEDs;

tLED – is a total LEDs.

The algorithm of the code is very difficult, so there will be general algorithm only for 3 blocks (other blocks acted in the same manner).

- 1. Begin. Here we initialize ports and variables (including variable "life=3");

- 2. Then our program checks variable "life", if it not equal to zero. If it is, our program ends. If our variable "life" is not equal to zero, there will be checked block1;

- 3. Block1. In this block, there will be check ports B and D for a equality. If ports not equal, then our variable "life" will be decrement and our program goes to item 2. If ports are equal, then our program will check variable "life":

- 4. If variable "life" is equal to zero, program will be terminated. If variable "life" is not equal to zero, our program goes to block2;

- 5. Block2. If ports D and B not equal, then our variable "life" will be decrement and our program goes to item 4. If ports are equal, then our program will check variable "life";

- 6. If variable "life" is equal to zero, program will be terminated. If variable "life" is not equal to zero, our program goes to block 3;

- 7. Block3. If ports D and B not equal, then our variable "life" will be decrement and our program goes to item 6. If ports are equal, then our program will end.

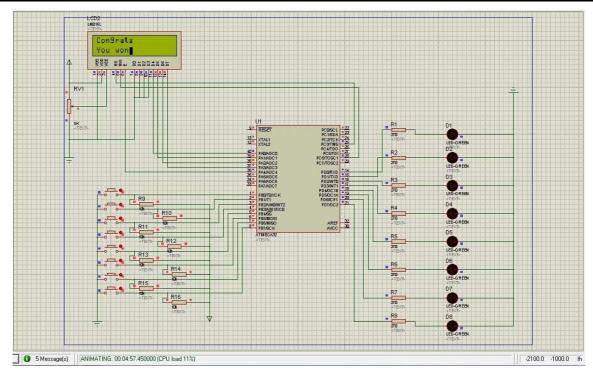

#### Electric scheme of the device

Electric scheme of DMTT device is shown on fig. 5.

Fig. 4. General block-scheme of the program

Fig. 5. Electric scheme of DMTT device

# **Memory tester**

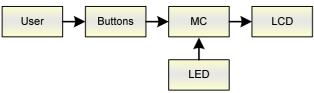

Memory tester consists on buttons, LEDs (light-emitting diodes), microcontroller ATmega32 and LCD module HD44780. The structural scheme is shown at fig. 6.

The sense of device is, that in a random order LEDs are turn on. After LEDs are blow out, the user have to repeat the order of LEDs. There are 10 difficulties in a test. Most hard is the last one. User has 3 tries, after this he will lose and LCD module will show the result of user's activity. The result is calculated by formula:

result=

$$\frac{\text{pLED}}{\text{tLED}}$$

100%,

where, pLED – is a passed LEDs;

tLED – is a total LEDs.

Fig. 6. Structural scheme of memory tester

## LCD module

The controller is made by Hitachi HD44780 is actually the industry standard and widely used in the manufacture of alphanumeric LCD modules. Analogs of the controller or compatible with the interface and

the command language of chips, producing a set of firms, including: Epson, Toshiba, Sanyo, Samsung, Philips. An even larger number of firms produce LCD modules based on data controllers. These modules can be found in a variety of devices: measuring instruments, medical and industrial equipment, office equipment – printers, phones, faxes and copiers.

Alphanumeric LCD modules are cheap and easy solution to save time and resources when developing new products, while providing a mapping of a large amount of information with good legibility and low power consumption. The possibility of equipping the LCD backlight modules enables them to operate in environments with low or no lighting, and the version with extended temperature range (-20° C. ... +70° C) in difficult operating conditions, including a portable, field and even, sometimes, on-board equipment.

HD44780 controller can potentially operate with 2 lines of 40 characters each (for modules with 4 lines of 40 characters uses two identical controllers), the matrix character 5×7 points. Controller also supports characters with 5×10 matrix of pixels, but in recent years, the LCD modules with a matrix almost never occur, so we can assume that in fact there are only the characters 5×7 points.

In our case, there was created the addition driver for LCD module. With the help of it, we can configure LCD module however. For example, with the help of this part code we can connect LCD to any i/o port we want.

#define LCD\_DATA A

//Port PA0-PA3 are connected to D4-D7

#define LCD\_DATA\_POS 0

#define LCD\_E A

//Enable/strobe signal

#define LCD\_E\_POS PA4

//Position of enable in above port

#define LCD\_RS C //RS SIGNAL

#define LCD\_RS\_POS PC3

#define LCD\_RW C //RW SIGNAL

#define LCD\_RW\_POS PC6

But, we have still remember, that The LCD data lines D4 to D7 must be connected to consecutive pins starting from LCD\_DATA\_POS. Set LCD\_DATA to the port where you have connected the LCD data lines. Then set LCD\_DATA\_POS to the starting pin of data lines.

Also, we have an opportunity to set the number of rows and number of digits in these rows.

## **Results of DMTT practical testing**

After DMTT construction its functions and suitability were tested for the solution of practical tasks. Memory test also was applied practically. The sense of memory testing (training) for patient (or for training of healthy person) is in necessity to memorize (and to repeat) some results of combination of

little light indicators flashes. There are 8 little light indicators, 8 buttons and a little screen for comments at frontal panel of the device. Following data were taken into account for light indicators activity combination: quantity of burned indicators, their order, flash time length and pause length between flashes. After each series demonstration the patient had to press buttons respectively to notice series. Flashes, their order and length, and the length of pauses were changed during the time of testing/ Test difficulties the speed of changes - were increased from level to level. 10 levels of training may be realized during experiment; the 1-st level is the easiest one, the 10-th level is the most difficult. Tested person may pick up by himself the suitable level and make it higher at the next step. A doctor also may suggest the suitable level for trained patient. Wrong patient answers make the total score of the test lower; nevertheless he may continue the test, but the increase of errors numbers leaded to the end of the test.

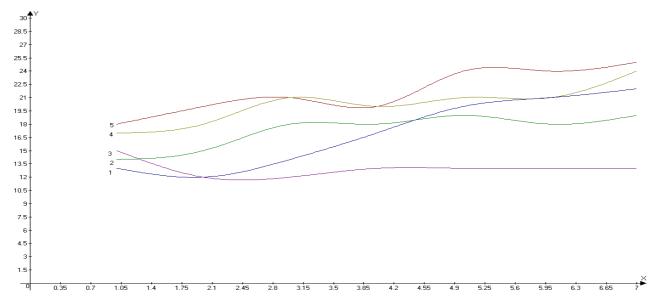

During one week, 5 stochastically picked healthy people participated in DMTT testing. Each of them was trained using memory test during 15 min every day. Results of experiments with memory testing are shown on fig. 7. Five curves correspond to results of 5 persons testing. It is possible to see that the index of first person memory was the worst. But although his index after passing the experiment isn't the best, he demonstrated the best results of training during the experiment.

Fig. 7. Results of experiments with memory testing and training

### **Conclusions**

Present work started from profound examination of memory items and analogues devices for memory testing. Finally device was developed and following conclusions may be done at the end of this work. 1. Effective and portable device for testing and training of visual memory and reaction was constructed. According to work procedure the device was done on the basis of ATmega32 microcontroller with the help of AVR Studio environment.

- 2. Full package of program supply was elaborated. Program code written for this device contains more then 5100 rows. The Atmel AVR ATmega32 is supported with a full suite of program and system development tools, including C compilers, macro assemblers, program debugger/simulators, In-Circuit Emulators, and evaluation kits.

- 3. Device demonstrated good results during it practical testing. 4 tested persons from 5 improved indices of their memory during these tests.

- 4. Fulfilling our work we tried to do this for improving of memory of common people, to perfect memory of children and, in future, to cure patients with brain damages and amnesia. For example, in case of tracing of person's memory state it is possible to notice even slight memory changes with years with the aim to support it on stable level.

- 5. Developed device for testing and training of visual memory and reaction is inexpensive.

- 6. Developed device and methods could be suitable for different practical applications in different spheres: medicine, sport, military etc.

# References

- 1. *Olson, Harry F.* 1967. Music, Physics and Engineering. Dover Publications. P. 248–251.

- 2. Oppenheim, Alan V., Schafer, Ronald W. 1975. Digital signal processing. Englewood Cliffs, N.J.: Prentice-Hall. P. 548–554.

- 3. *Proakis, J. G. and Manolakis, D. G.* 1996. Digital Signal Processing, Upper Saddle River, N.J.: Prentice-Hall. P. 910–913.

- 4. *Samarin*, A. 2004. Architecture of TFT LCD panels for monitors and notebook. Components and technology. No. 3. P. 78–86. (in Russian).

Received 14 October 2013

Klyuchko Olena Mychailivna. Ph.D. in Biological Sciences (biophysics). Docent.

Aeronavigation Institute, National Aviation University, Kyiv, Ukraine.

Education: Taras Schevchenko National University (1981), National Aviation University (2003), Kyiv, Ukraine.

Research area: biophysics, brain sciences, bioinformatics, ecology.

Publications: 118. E-mail: iesy@nau.edu.ua

# Tsal-Tsalko Vitaliy Ivanovych. Bachelor of technical sciences.

Aviation Computer Integrated Complexes Department, National Aviation University, Kyiv, Ukraine.

Education: National Aviation University (2012)

Research interests: programming, computer sciences, economy.

Publications: 0.

E-mail: iesy@nau.edu.ua

# О. М. Ключко, В. І. Цал-Цалко. Пристрій та програмне забезпечення для тренування візуальної пам'яті людини на базі мікроконтролера ATmega32

Наведено дані щодо створення нового пристрою з повним пакетом відповідних програм для тестування і тренування візуальної пам'яті. Пристрій створено на базі мікроконтролера ATmega32 та середовища AVR Studio. Ключові слова: пристрій для тестування пам'яті; ATmega32 мікроконтролер; програмне забезпечення; середовище AVR Studio.

## Ключко Олена Михайлівна. Кандидат біологічних наук (біофізика). Доцент.

Інститут аеронавігації, Національний авіаційний університет, Київ, Україна.

Освіта: Національний університет імені Тараса Шевченка, Київ (1981), Національний авіаційний університет (2003).

Напрям наукової діяльності: біофізика, науки про мозок, біоінформатика, екологія.

Кількість публікацій: 118. E-mail: iesy@nau.edu.ua

# Цал-Цалко Віталій Іванович. Бакалавр.

Інститут аеронавігації, Національний авіаційний університет, Київ, Україна.

Освіта: Національний авіаційний університет, Київ, Україна (2012).

Напрямок наукової діяльності: програмування, комп'ютерні науки, економіка.

Кількість публікацій: 0. E-mail: <u>iesy@nau.edu.ua</u>

# Е. М. Ключко, В. И. Цал-Цалко Устройство и программное обеспечение для тренировки визуальной памяти человека на базе микроконтроллера ATmega32

Приведены данные о создании нового устройства с полным пакетом соответствующих программ для тестирования и тренировки визуальной памяти. Устройство создано на базе микроконтроллера ATmega32 и среда AVR Studio.

**Ключевые слова:** устройство для тестирования памяти; ATmega32 микроконтроллер; программное обеспечение; среда AVR Studio.

## Ключко Елена Михайловна. Кандидат биологических наук (биофизика). Доцент.

Институт аэронавигации, Национальный авиационный университет, Киев, Украина.

Образование: Национальный университет имени Тараса Шевченко, Киев (1981), Национальный авиационный университет (2003).

Направление научной деятельности: биофизика, науки о мозге, биоинформатика, экология.

Количество публикаций: 118.

E-mail: iesy@nau.edu.ua

# Цал-Цалко Виталий Иванович. Бакалавр.

Институт аэронавигации, Национальный авиационный университет, Киев, Украина.

Образование: Национальный авиационный университет, Киев, Украина (2012).

Направление научной деятельности: программирование, компьютерные науки, экономика.

Количество публикаций: 0.

E-mail: iesy@nau.edu.ua